## What does AVR RISC mean?

- The acronym AVR has been reported to stand for: Advanced Virtual RISC

- RISC stands for reduced instruction set computer.

- CPU design with a reduced instruction set as well as a simpler set of instructions (like for example PIC and AVR)

- Harvard architecture

- □ separate bus for program and data memory

## **AVR 8-Bit RISC High Performance**

True single cycle execution

single-clock-cycle-per-instruction execution

PIC microcontrollers take 4 clock cycles/instruction

One MIPS (mega instructions per second) per MHz (up to 20 MHz clock).

32 general purpose registers

provide flexibility and performance when using high level languages

prevents access to RAM

### **AVR 8-Bit RISC Low Power Consumption**

## 1.8 to 5.5V operation

□ will use all the energy stored in your batteries

- A variety of sleep modes

- AVR Flash microcontrollers have up to six different sleep modes

- □ fast wake-up from sleep modes

- Software controlled frequency

## **AVR 8-Bit RISC Compatibility**

- AVR® Flash microcontrollers share a single core architecture

- □ use the same code for all families

- □ 1 Kbytes to 256 Kbytes of code

- □ 8 to 100 pins

- all devices have Internal oscillators

## **AVR 8-Bit RISC family**

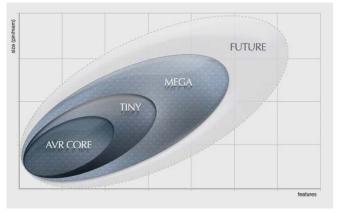

### tinyAVR

□ 1-16 KBytes Flash, 8-32 pin

## megaAVR

- □ 4-256 KBytes Flash, 28-100 pin

- □ Extended instructions (multiplication)

## XMEGA

- □ 16-384 KBytes Flash, 44-100 pin

- □ Extra: DMA, coding support

## AVR ASIC

□ megaAVR with LCD, USB, CAN interfaces.

## Most Importantly!!!

- Best C compiler to start programming in C

and it is FREE

- Code Vision AVR

http://www.hpinfotech.ro/

- AVR Studio 4 also free from:

http://www.atmel.com/dyn/products/tools\_card.asp?tool\_id=2725

## **ATmega16A features**

Advanced RISC Architecture

- 131 Powerful Instructions Most Single-clock Cycle Execution

- □ 32 x 8 General Purpose Working Registers

- □ Up to 16 MIPS at 16 MHz

- □ On-chip 2-cycle Multiplier

# ATmega16A features

- Memory segments

- 16K Bytes of In-System Self-programmable Flash program memory

- 512 Bytes EEPROM (Electrically Erasable Programmable Read-Only Memory)

- IK Byte Internal SRAM (Static Random Access Memory)

- □ Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

## **ATmega16A** features

## Peripheral features

- Two 8-bit Timer/Counters and one 16-bit Timer/Counter with Separate Prescalers, Compare Mode and Capture Mode

- □ Real Time Counter with Separate Oscillator

- □ Four PWM Channels

- □ 8-channel, 10-bit ADC

# **ATmega16A features**

Peripheral features

- □ Byte-oriented Two-wire Serial Interface

- Programmable Serial USART

- □ Master/Slave SPI Serial Interface

- Programmable Watchdog Timer

- On-chip Analog Comparator

## **ATmega16A features**

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- □ Six Sleep Modes

## **ATmega16A features**

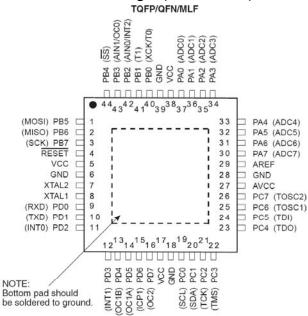

| I/O and Packages                                     |

|------------------------------------------------------|

| 32 Programmable I/O Lines                            |

| $\Box$ 40-pin PDIP, 44-lead TQFP, and 44-pad QFN/MLF |

| Operating Voltages                                   |

| 2.7 - 5.5V for ATmega16A                             |

| Power Consumption (1 MHz, 3V, and 25°C)              |

| □ Active: 0.6 mA                                     |

| □ Idle Mode: 0.2 mA                                  |

|                                                      |

Plastic Dual Inline Package (PDIP)

|                                                                                                                                                                                                                                                                                      | PDI                                                                                                         | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| (XCK/T0) PB0 [<br>(T1) PB1 [<br>(INT2/AIN0) PB2 [<br>(OC0/AIN1) PB3 [<br>(S5) PB4 [<br>(MOS1) PB5 [<br>(MIS0) PB6 [<br>(SCK) PB7 [<br>RESET [<br>VCC [<br>GND [<br>XTAL2 [<br>XTAL2 [<br>(RXD) PD0 [<br>(INT0) PD2 [<br>(INT0) PD1 [<br>(INT0) PD2 [<br>(INT1) PD3 [<br>(ICP1) PD6 [ | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20 | 40         PA0 (ADC0           39         PA1 (ADC1           38         PA2 (ADC2           37         PA3 (ADC3           36         PA4 (ADC4           35         PA3 (ADC3           36         PA4 (ADC4           35         PA5 (ADC5           34         PA6 (ADC6           33         PA7 (ADC7           30         PA7CC           29         PC7 (TOSC           28         PC6 (TOSC           27         PC5 (TDI)           26         PC4 (TDO)           25         PC3 (TMS)           24         PC2 (TCK)           23         PC1 (SDA)           22         PC0 (SCL)           21         PD7 (OC2) | )<br>))<br>))<br>)) |

- Thin Profile Plastic Quad Flat Package (TQFP)

- Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF)

## **Pin Configurations**

- VCC Digital supply voltage

- GND Ground

- Port A (PA7:PA0)

- □ analog inputs to the A/D Converter

- 8-bit bi-directional I/O port (if the A/D Converter is not used)

- Port B (PB7:PB0)

- □ 8-bit bi-directional I/O port

- functions of various special features

#### Port C (PC7:PC0)

- □ 8-bit bi-directional I/O port

- JTAG interface (Standard Test Access Port and Boundary-Scan)

15

## **Pin Configurations**

#### Port D (PD7:PD0)

- □ 8-bit bi-directional I/O port

- □ functions of various special features

#### RESET

□ Reset Input. A low level active

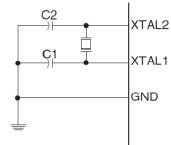

#### XTAL1, XTAL2

oscilator pins

### AVCC

the supply voltage pin for Port A and the A/D Converter

#### AREF

□ analog reference voltage for ADC

|                                                                                                                                                                                                                                                             | PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (XCK/T0) PB0 [<br>(T1) PB1 [<br>(INT2/AIN0) PB2 [<br>(OC0/AIN1) PB3 [<br>(MOSI) PB5 [<br>(MOSI) PB5 [<br>(MOSI) PB6 [<br>(SCK) PB7 [<br>RESET [<br>VCC [<br>GND [<br>XTAL1 [<br>(RXD) PD0 [<br>(INT0) PD1 [<br>(INT1) PD3 [<br>(OC1B) PD4 [<br>(ICP1) PD6 [ | 1       40       PA0 (ADC0)         2       39       PA1 (ADC1)         3       38       PA2 (ADC2)         4       37       PA3 (ADC3)         5       36       PA4 (ADC4)         6       35       PA6 (ADC6)         8       33       PA7 (ADC7)         9       32       AREF         10       31       GND         11       30       AVCC         12       29       PC7 (TOSC2)         13       28       PC6 (TOSC1)         14       27       PC5 (TDI)         15       26       PC3 (TKS)         17       24       PC2 (TCK)         18       23       PC1 (SDA)         19       22       PC0 (SCL)         20       21       PD7 (OC2) |

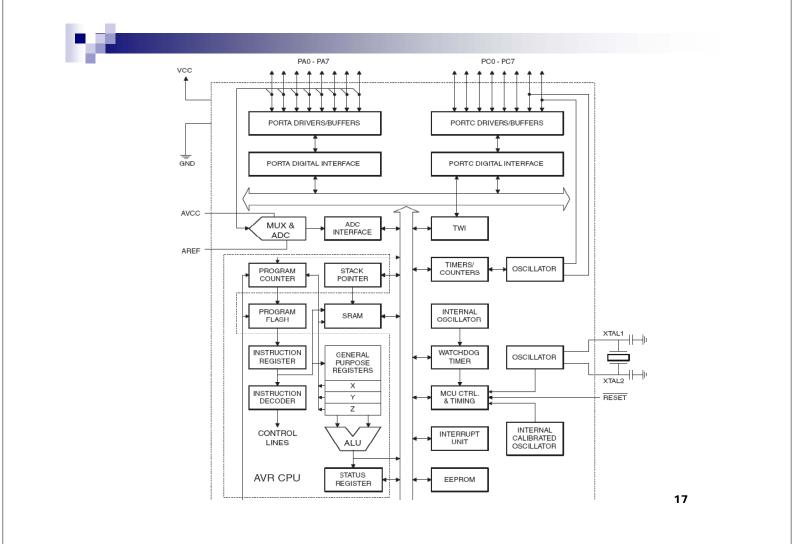

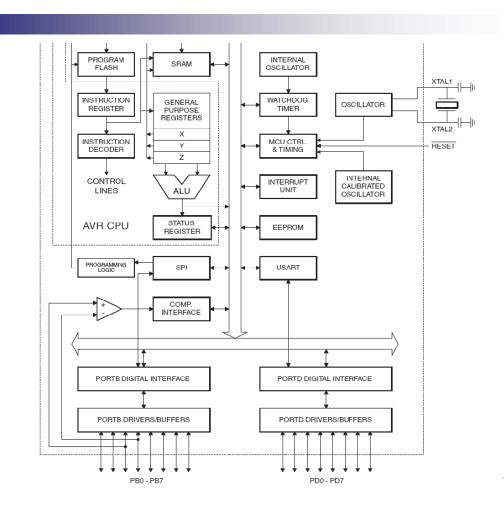

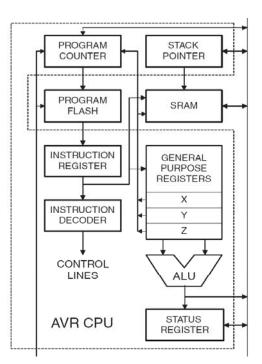

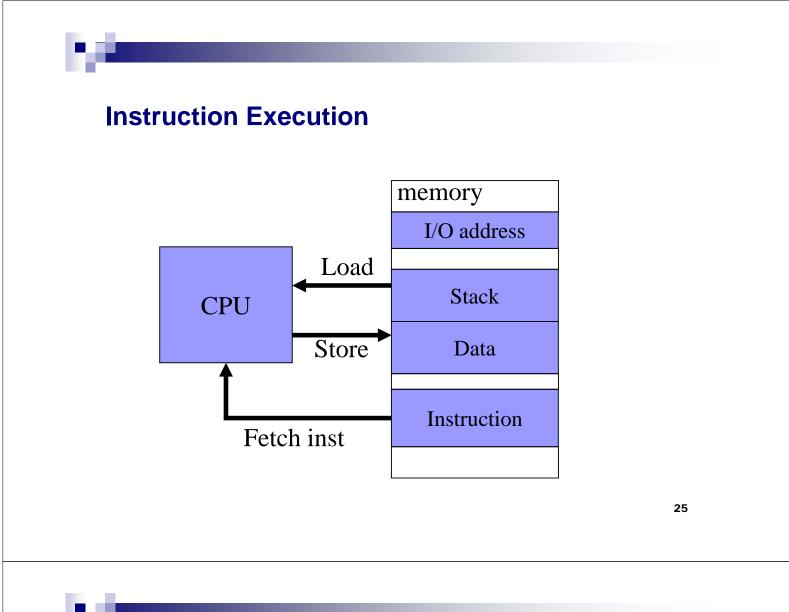

## **AVR CPU**

- AVR uses a Harvard architecture

- separate memories and buses for program and data

- The program memory is In-System Reprogrammable Flash memory

- 32 x 8-bit general purpose registers

- single-cycle Arithmetic Logic Unit (ALU) operation

- 6 registers can be used as three 16bit indirect address register pointers

## **Status Register**

| Bit                                      | 7                                                                                                                                                                                                                                                                                                         | 6   | 5   | 4                 | 3                                                       | 2                              | 1                                        | 0   | _    |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------|---------------------------------------------------------|--------------------------------|------------------------------------------|-----|------|

|                                          | I                                                                                                                                                                                                                                                                                                         | Т   | Н   | S                 | V                                                       | N                              | Z                                        | С   | SREG |

| Read/Write                               | R/W                                                                                                                                                                                                                                                                                                       | R/W | R/W | R/W               | R/W                                                     | R/W                            | R/W                                      | R/W | -    |

| Initial Value                            | 0                                                                                                                                                                                                                                                                                                         | 0   | 0   | 0                 | 0                                                       | 0                              | 0                                        | 0   |      |

| Enab<br>1=<br>Bit 6<br>So<br>op<br>Bit 5 | <ul> <li>Bit 7 – I: Global Interrupt<br/>Enable <ul> <li>1=enable, 0=disable interrupts</li> </ul> </li> <li>Bit 6 – T: Bit Copy Storage <ul> <li>source or destination for the operated bit</li> </ul> </li> <li>Bit 5 – H: Half Carry Flag <ul> <li>Bit 4 – S: Sign Bit, S = N⊕V</li> </ul> </li> </ul> |     |     | Ove<br>Bit<br>Bit | erflow I<br>2 – N: I<br>1=negat<br>1 – Z: 2<br>1=zero i | Negativ<br>tive,0=p<br>Zero FI | <b>ve Flaç</b><br>ositive r<br><b>ag</b> | J   |      |

21

## **General Purpose Register File**

| 7 0 | Addr. |

|-----|-------|

| R0  | \$00  |

| R1  | \$01  |

| R2  | \$02  |

|     |       |

| R13 | \$0D  |

| R14 | \$0E  |

| R15 | \$0F  |

| R16 | \$10  |

| R17 | \$11  |

|     |       |

| R26 | \$1A  |

| R27 | \$1B  |

| R28 | \$1C  |

| R29 | \$1D  |

| R30 | \$1E  |

| R31 | \$1F  |

- One 8-bit output operand and one 8-bit result input

- Two 8-bit output operands and one 8-bit result input

- Two 8-bit output operands and one 16-bit result input

- One 16-bit output operand and one 16-bit result input

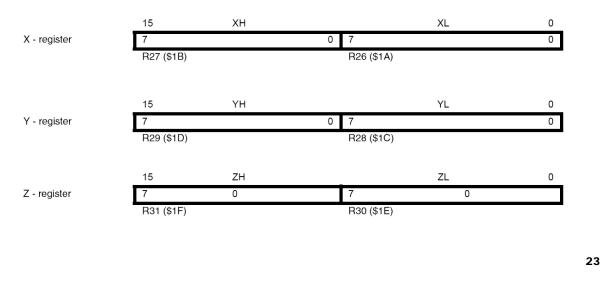

X-register Low Byte X-register High Byte Y-register Low Byte Y-register High Byte Z-register Low Byte Z-register High Byte

## The X-register, Y-register and Z-register

The registers R26:R31 can be used as 16-bit address pointers for indirect addressing of Data Space

## **Major Instruction Types**

### Arithmetic and logic:

- $\Box$  add, subtract, multiply;

- □ and, or, not, xor

## Data movement:

□ transfer data between registers and/or memories

## Control:

□ Branches and jumps

## **Register Instructions**

Data copying mov r4, r7

Immediate values ldi r16, 5 ori r16, 0xF0 andi r16, 0x80 subi r20, 1

## **Register Instructions**

Arithmetic and Logic registers operations add r1, r2 or r3, r4 lsl r5 mul r5, r18 ; r1:r0 = r5\*r18 rol r7 ror r9 inc r19 dec r17

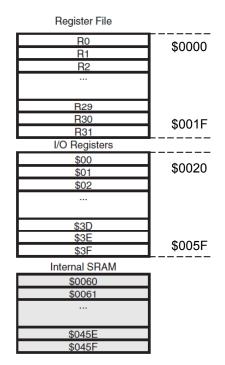

### **AVR Data Memory**

- 32 general purpose working registers,

- 64 I/O Registers,

- 1024 bytes of internal data SRAM

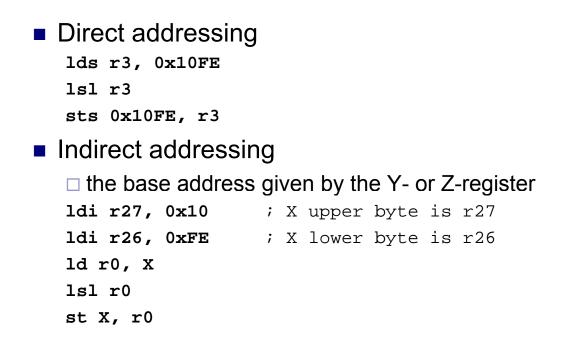

## **Data memory instructions**

# Data memory instructions

Indirect addressing modes with automatic predecrement and post-increment

| ld r0, | X+ ; | memory access at address X,     |

|--------|------|---------------------------------|

|        | ;    | then X is incremented           |

| ld r0, | +X ; | X is incremented                |

|        | i    | then memory access at address X |

| ld r0, | х-   |                                 |

| ld r0, | -X   |                                 |

|        |      |                                 |

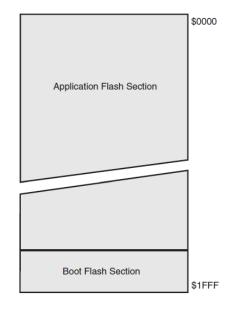

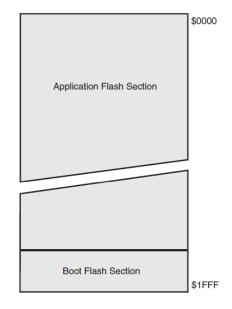

## **AVR Program Memory**

- 16K bytes On-chip Flash memory for program storage

- Organized as 8K x 16

- Divided into two sections,

- Boot Program sectio

- □ Application Program section

- At least 10,000 write/erase cycles

## **AVR Program Memory**

Read

#### BYTE access

□ Addressing by Z pointer

LPM r5, Z LPM r5, Z+

\_\_\_\_\_

LPM ; r0 este destinatie, ; Z adresa

#### Write – word only SPM ; PM(Z) <= R1:R0</p>

# **Clock signal** A clock signal is a square wave of fixed frequency f<sub>CK</sub> Often, transitions will occur on one of the edges of clock pulses □ the rising edge Positive-going Negative-going transition (PGT) transition (NGT) □ the falling edge Time (a)

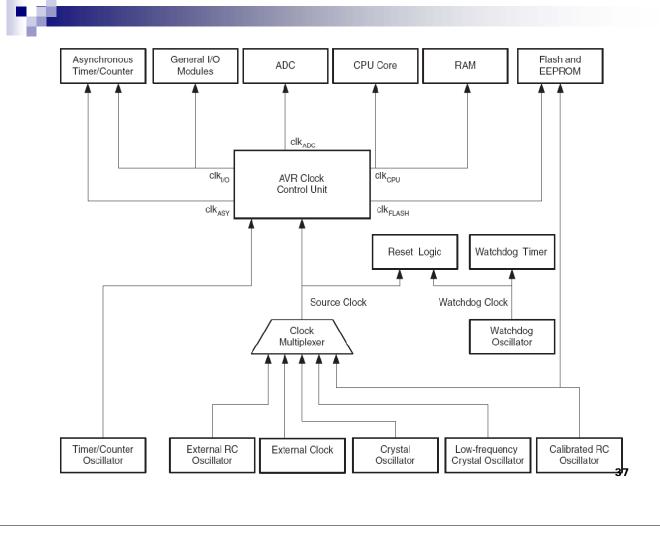

## **Clock Sources – AVR uC**

- External Crystal/Ceramic Resonator

- External Low-frequency Crystal

- External RC Oscillator

- Calibrated Internal RC Oscillator

- External Clock

## **Clock Sources – AVR uC**

□ watch crystal 32.768 kHz

External Crystal/Ceramic Resonator □ 0.4 - 0.9 MHz (Ceramic Resonator) 0.9 - 3.0 MHz □ 3.0 - 8.0 MHz  $\Box \leq 1.0 \text{ MHz}$ External Low-frequency Crystal

35

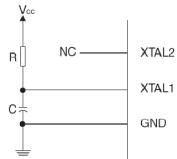

### Clock Sources – AVR uC

External RC Oscillator NC -R 0.1 - 0.9 MHz 0.9 - 3.0 MHz □ 3.0 - 8.0 MHz □ 8.0 - 12.0 MHz Calibrated Internal RC Oscillator □ 1 MHz (default), 2 MHz, 4 MHz or 8 MHz External Clock Drive □ aplicat direct pe pinul XTAL1